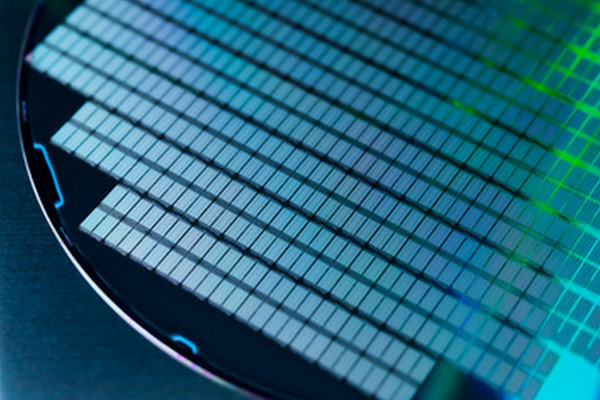

Chip Production

Continuously optimize SoC production with predictive analytics and adaptive insights, from product ramp through high-volume manufacturing.

Continuously optimize SoC production with predictive analytics and adaptive insights, from product ramp through high-volume manufacturing.

From single die to full production population.

The crystal ball for your production. Powered by data, not magic.

Cloud analytics for New Product Introduction (NPI) of advanced semiconductors.

Explore our silicon proven examples – just a few of many use cases.

Apples-to-apples correlation of post-silicon measurements back to pre-silicon models to quickly validate assumptions, resolve discrepancies, and accelerate bring-up.

Identify the optimal mix of dies, wafers, or lots by analyzing parametric signatures, device behavior, and variability to ensure the right material enters each stage.

Monitor in-situ performance drift and degradation during HTOL to uncover early reliability risks and validate long-term device behavior.

Compare key metrics across product generations or design variants to uncover trends, validate improvements, and drive faster learning cycles.

Quantify the coverage and effectiveness of functional tests using deep-data metrics to reveal blind spots and ensure robust validation.

Correlate data across multiple stages and test types to identify systemic issues, improve test efficiency, and accelerate root-cause analysis.

Edge-to-cloud analytics for production insight at high-volume manufacturing test

Design-aware, guided analytics with a production cockpit and pre-built journeys.

Die, wafer, and lot population analysis

In-test software applications run adaptive algorithms in near real-time.

Catch latent defects before they make it to the field, with ML-based and per-die detection of production anomalies at test.

Reduce DPPM, prevent Silent Data Corruption and enhance Functional Safety with proteanTecs outlier detection techniques

Compare measured IDDQ against predicted values to confidently prevent quality escapes without compromising yield. Faulty dies are flagged as early as wafer sort, enabling proactive screening and smarter downstream decisions.

Identify outliers with marginal or latent defects through advanced margin quantification of millions of path delays, delivering rich parametric visibility. Gain early detection of suspect dies with increased visibility.

Gain powerful analytics and insights on production quality with stage-to-stage correlation analysis that connects data across the entire test flow. Accelerate RMA investigations and resolution through deep visibility into root causes.

Compare measured IDDQ against predicted values to confidently prevent quality escapes without compromising yield. Faulty dies are flagged as early as wafer sort, enabling proactive screening and smarter downstream decisions.

Identify outliers with marginal or latent defects through advanced margin quantification of millions of path delays, delivering rich parametric visibility. Gain early detection of suspect dies with increased visibility.

Gain powerful analytics and insights on production quality with stage-to-stage correlation analysis that connects data across the entire test flow. Accelerate RMA investigations and resolution through deep visibility into root causes.

Learn more about outlier detection

This paper introduces proteanTecs groundbreaking Outlier Detection solution that eliminates that tradeoff. proteanTecs' Outlier Detection uses deep data analytics and ML to detect latent defects as early as Wafer Sort, achieving high fault detection accuracy by learning normal behavior with on-chip agents and comparing test measurements with predicted ones. It identifies marginal issues beyond simple pass/fail metrics, where traditional methods fail.

Fabless chipmaker boosted quality with telemetry-based machine learning in IDDQ testing

Leverage deep in-chip telemetry and machine learning to accurately predict VDDmin for static per-die VDD setting and tune operational settings at system test.

Personalized assessment

Lower max-power

Test time reduction

Cost reduction

Telemetry and ML-based

Inline decisions at test

Predicts VDDmin using Profiling & Classification Agents, sensitive to process variance across all transistor types and standard cells.

A deep data machine learning solution allowing minimal steps for unmatched accuracy. Save time with only 1-2 search steps, instead of the conventional multi-step VDDmin shmoo.

ML models are training on characterization data collected – leveraging Agent fusion, statistical analysis and advanced algorithms. Once validated, the training models are deployed to the edge software on the tester.

Integrates seamlessly into the test program and provides assessment on the test floor for real-time decisions.

Reduce VDDmin guard band between ATE, SLT and System Test based on timing-margin measurement.

Gain visibility into operational and environmental conditions, real workloads vs. structural test, and effects of voltage regulator and power supply.

Turn process variation into competitive advantage with intelligent, fine-grained power and performance binning based on true silicon characteristics.

Classify each chip with precision

Optimize power and performance per die

Enable smarter segmentation

This paper introduces proteanTecs groundbreaking Outlier Detection solution that eliminates that tradeoff. proteanTecs' Outlier Detection uses deep data analytics and ML to detect latent defects as early as Wafer Sort, achieving high fault detection accuracy by learning normal behavior with on-chip agents and comparing test measurements with predicted ones. It identifies marginal issues beyond simple pass/fail metrics, where traditional methods fail.

In this webinar we describe and quantify the benefits of using deep data analytics to accelerate SoC product development. Rich Wawrzyniak of Semico Research presents a head-to-head comparison of two companies designing a similar multicore SoC on a 5nm technology node.

Identify early indicators of risk by analyzing timing margin data from within the chip.

Discover how the fabless chipmaker used proteanTecs on-tester and cloud analytics to prevent a flood of RMAs with ML-powered spatial analysis

This webinar highlights PDF Solutions’ semiconductor big data analytics solutions with proteanTecs’ deep data offering for chip and system lifecycle analytics to enable data-driven actionable insights for new product introduction.

June Paik • CEO, FuriosaAI

Mohit Gupta • SVP and GM, Custom Silicon and IP, Alphawave

Eddie Ramirez • VP of Go-to-Market, Infrastructure Line of Business, Arm

Dr. Charlie Su • CTO and President, Andes Technology

Ran Schrift • Director of Operations, Xsight Labs

Sue Ryu • CEO, SAPEON

Kalyan Mulam • SVP of ASIC Engineering, Astera Labs

Rich Wawryzniak • Principal Analyst, Semico

Andrzej Strojwas • CTO, PDF Solutions

Get answers to common questions about how proteanTecs improves quality, reduces power, and enhances performance, all while ensuring reliable, cost-efficient production.

The Chip Production Solution is a comprehensive suite of applications that leverage proteanTecs’ deep data analytics to optimize semiconductor manufacturing from ramp to high-volume production. It combines on-tester software and a cloud-based platform to deliver predictive insights for quality, power, yield, and performance optimization.

It addresses key challenges in semiconductor production such as outlier escapes, test inefficiency, yield loss, and variability across lots or sites. By detecting latent defects, predicting performance, and enabling adaptive process control, it helps manufacturers confidently improve product quality and throughput while reducing operational costs.

proteanTecs’ agents embedded in the chip generate rich parametric data. This data is processed by on-tester software running ML-trained models and algorithms in near real time. The cloud platform then correlates insights across devices, lots, and stages, providing a closed-loop analytics system that continuously learns and adapts.

The solution provides APIs and data connectors for seamless integration with ATEs and analytics tools. On-tester software runs inline without disrupting test flow, and cloud analytics can be deployed in flexible architectures to align with customer IT and security policies.